# MMR Multichannel Readout

32 to many 1000 channels detector readout system

(Data sheet V1.2)

**MMR Multiplexed Readout** is a platform for multiplexed readout of large arrays of silicon detectors MWPCs or other charge generating particle detectors. It consist of a master board, which performs time multiplexing, analogue to digital conversion, data storage and triggered data transmission via optical link to a central data collector module. The board provides a local clock, which is synchronised by the VME master to a central time. Timestamp resolution is 1ns (starting from 2021).

### Hardware features:

### Modular Setup

- miniaturised detector front ends optical Link

- Up to 128 channels per front end

- Large data buffer on front end

- Amplifier, filter and digitization on front end

- Self triggering

- Possible ranges:

- $\circ$  500 keV to 100 GeV (1 GeV = 45 pC)

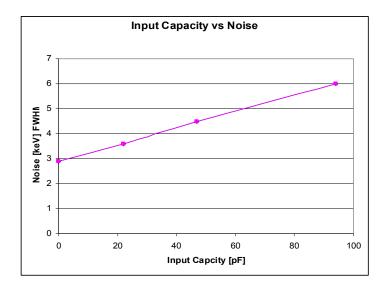

- Noise < 3 keV FWHM for 0 pF input cap.

### Front end synchronisation to a central clock

- time stamping in front end, 1ns resolution

- absolute time stamping allows to buffer the data at the front end without loss of timing information

### • Easy to handle Optical POF fiber bus

- Only standard lab tools required to assemble the fibers

- Inexpensive twin fibers available

- Fast 200 Mbit front end bus

- Up to 50 m with POF fibers

- Works with a single +6.0 V to +8.0 V supply Easy galvanic separation of front end

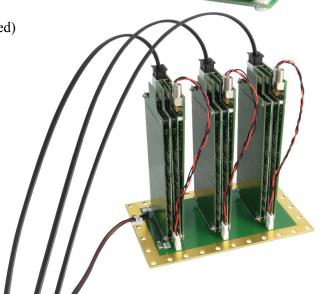

Up to 2048 channels per VMMR-16 Stacked boards for 128 channels

$60 \, x140 \, x20 mm^3$

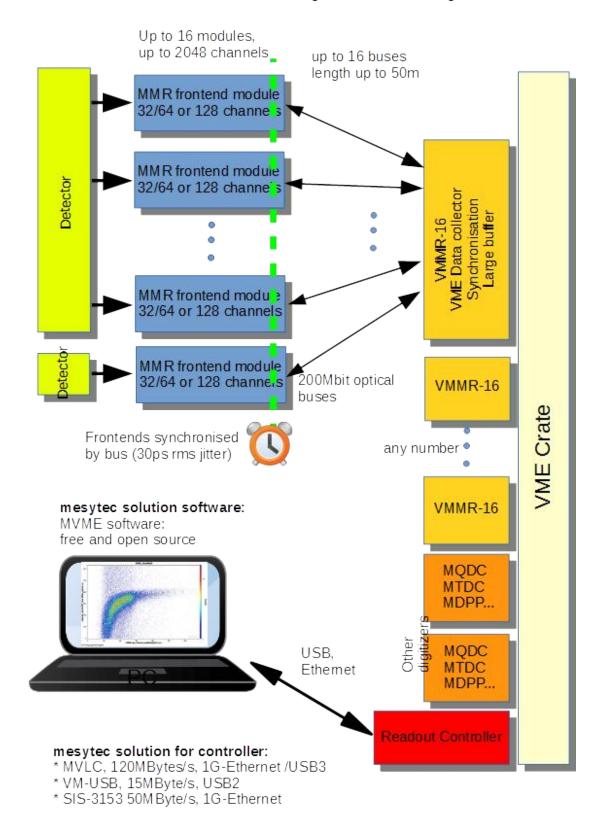

Overview: MMR – System

# Overview mesytec MMR-System

### **MMR Detector Front end module**

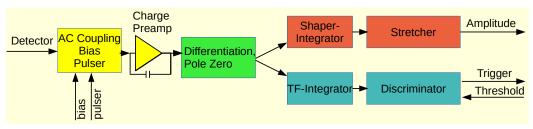

### **Analogue part:**

- Bias supply, pulser coupling

- low noise charge integrating pre-amplifier

- shaper stretcher stage

- timing filter with discriminator

32 channels each layer

At the input, the signals are AC coupled and biased via resistor to a defined detector voltage up to 250 V or ground. This eliminates effects of high detector leakage currents on the charge sensitive preamplifier, and allows to bias, for example Si strip detectors or Si PMTs.

A pulser coupling allows do apply a pulser and provides a full check of electronics from input to data acquisition. The charge sensitive preamplifier can be configured in a wide sensitivity range and delivers a tail pulse with up to 10 ns rises time. It has a high open loop gain and allows to integrate input load capacities of up to 1 nF.

The following differentiation stage also includes the PZ compensation and works as part of the shaping filter. The signals are now split to an amplitude path starting with a second order integrator and a stretcher. After the stretcher, a static amplitude is available for further multiplexing.

The timing path starts with a fast integrator followed by a discriminator. All discriminator signals of one bank are "Ored" and sent to the digitization.

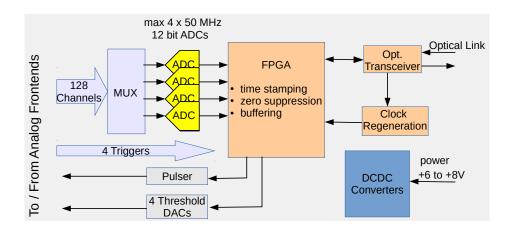

### Digital part:

- Digitisation: MMR-128 in 1.4 us, MMR-64 in 0.7 us.

- Synchronised clock

- Time stamping

- Zero suppression

- Buffering

- Generates pulser signals

Up to 128 amplitudes are multiplexed to 4 ADCs running with 50 MHz. This allows to convert 128 channels in 640 ns. The four input triggers from four banks start the readout and multiplexing sequence. The triggers are ored, and get a time stamp with a precision of 1 ns.

The trigger with time stamp is immediately sent via optical bus to the data collector module.

Converted amplitude pass a threshold filter to suppress non responding channels and reduce data.

The remaining channels are grouped to an event data structure and stored in a buffer.

The dead time is about the sum of shaping time + conversion time.

The event data are stored in the buffer until they are requested by the central data collector or a skip command is sent.

A fast 200 Mbit optical link, which is realised with optical POF (Plastic optical fibers) twin fibers transfers triggers, data and front end configuration data.

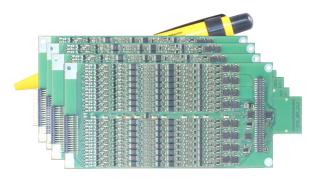

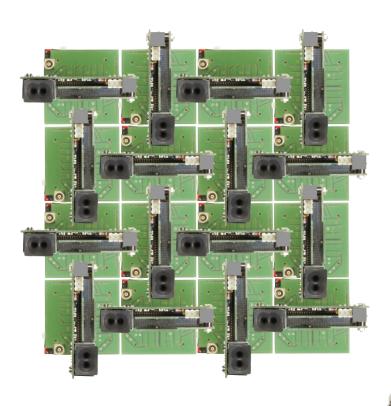

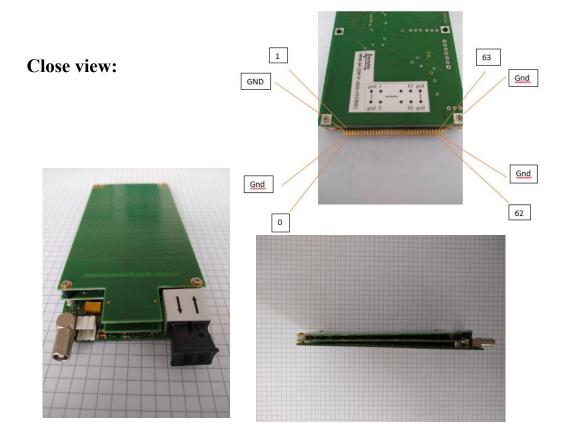

**Input** (detector) side of an MMR 128 channel pack. 2 x high density 68 pin connector with 1.27 mm pitch. Each connector 4 x ground + 64 channels.

Mating connectors:

Samtec CLP-134-02-F-D

Samtec SFMH-135-02-L-D (2 pins not connected)

### **Example:**

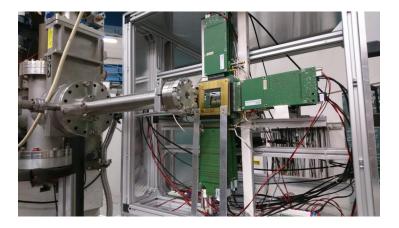

Detector board with 3 x MMR-128 for MWPC readout.

The VME receiver module VMMR-8 / VMMR-16 has 8 or 16 optical buses. With 16 buses, 8 of them are back on the motherboard.

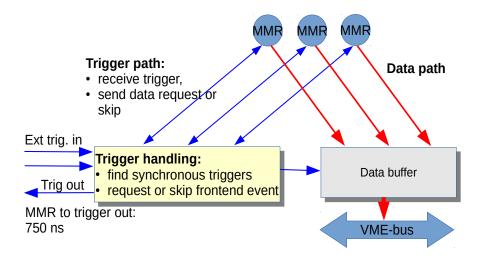

The module synchronises the front end clocks, receives triggers on the buses and accepts external gates.

- Live insertion (can be inserted in a running crate)

- Power consumption: 6.5 W

- + 5 V, 1.2 A

- 12 V, 50 mA.

### External trigger can be used to:

- · Get chopper time stamp

- · Synchronise events over several VMMR modules

### **Detailed functional description:**

The VMMR data collector module receives triggers from up to 16 MMR detector front ends. A trigger handling unit allows to define a trigger, groups of triggers and two external trigger input as source for an event generation. When an event is detected, the trigger time stamps are searched within a specified time (backward and forward in time) for coincident triggers. For coincident triggers the data from front end are requested, for non coincident a skip command is sent to the front end. All data which are now sent are formatted into an event structure and sent to a large buffer.

They are now ready for readout by the VME-bus.

The data structure format is 1) a header 2) a time stamp for each front end with valid data, amplitudes with channel address (front end address + channel address) for each responding channel. The end is marked by EOE marker including a global event data time stamp.

The data format is compatible to all other mesytec digitizer modules.

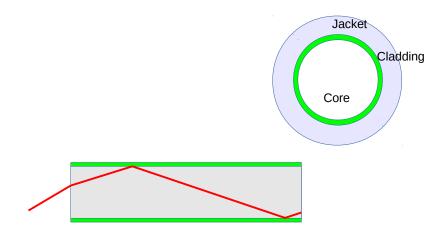

## **Optical Bus**

Used in industrial networks, car networks, consumer electronics. 1 mm diameter multi-mode fiber with step refraction index. Wave length 650 nm (red) -> inexpensive LEDs for transmitters.

#### **Facts:**

Core 980 um: PMMA (acrylic) refractive index 1.49 Cladding: 10 um silicone resin (refractive index 1.46)

Jacket 2.2 mm diameter.

Damping 0.2 dB/m (after 50m: 10% of light)

Up to 50 m of length with 200 Mbit/s (limited by dispersion)

Robustness under bending and stretching. Low power and compact Transceivers available

Easy to handle

Inexpensive (twin fiber: 2 Euro/m)

## **Possible front end configurations** (by population of the boards)

Gain: Full range: 50 fC to 100 pC

• Polarity:

pos / neg

• Shaping time:

150 ns to 5 us

• TF-time:

20 ns ... 1 us

• Channels

32 to 128 per front end package

• Mix of polarity and sensitivity on one front end module is possible

## **Realised Configurations:**

| Type                                 | Polarity              | Sensitivity      | TF time | Shaping time |

|--------------------------------------|-----------------------|------------------|---------|--------------|

| Si Strip detector,<br>Beta detection | positive and negative | 50 fC full range | 200 ns  | 1.5 us       |

| H8500-PMT +<br>Scintillator readout  | negative              | 100 pC           | 20 ns   | 100 ns       |

| H8500-PMT +<br>Scintillator readout  | negative              | 10 pC            | 20 ns   | 250 ns       |

| MWPC-readout                         | negative / positive   | 1 pC             | 200 ns  | 0.5 us       |

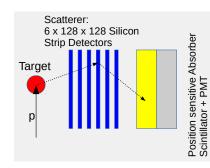

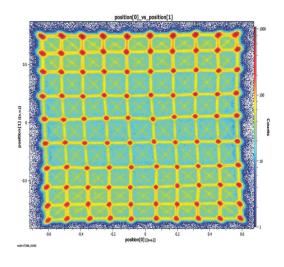

## **Readout of Silicon Strip Detectors and PMTs in coincidence:**

#### **Scatterer:**

- Energy in silicon typ. 140 keV (6.4 fC)

- Self triggering, threshold 15 keV

- MMR energy range 600 keV

- Noise 3 keV @ 0 pF (6 keV with detector)

- Readout:  $24 \times MMR-64 = 1536 \text{ Channels}$

- 24 optical buses  $\rightarrow$  2 x VMMR-16

#### Absorber:

• 8 x 8 multi anode PMT (H8500)

• Readout: MMR-64

### 1 MHz Gamma rate from Target:

Scatterer: 15 kHzAbsorber: 150 kHzCoincidences 15 kHz

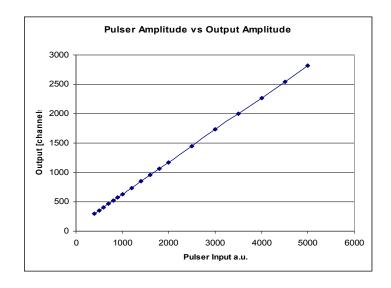

## Data for this most sensitive configuration:

Measurements with pulser at a 32 channel board,

configured for

- 600 keV maximum range

- 4k ADC conversion

- Shaping time 1.5 us

- TF-time 0.2 us

## Linearity:

The linearity is good, the channels are very homogeneous.

#### Noise:

Noise at 0 pF = 350 ENC

## Readout: LYSO 10 x 10 Scintillator with H8500 PMT

## H8500 readout, 64 channels (8 x 8 Anodes)

(also Si PMTs are equally suited)

- TF-time 20 ns, Shaping time 100 ns

- Polarity: negative

- dead time:  $\rightarrow$  700 ns

- Peak rate per 64 channel Front end: 0.4 MHz @ 75 % live time

- 4 x 4 system, average rate 6.5 MHz

- Sensitivity 100 pC maximum

- LYSO 10 x 10 crystals

- pitch 4 x 4 mm

- 22 Na Source, (511 keV Gammas)

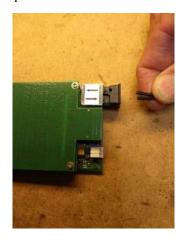

## How to connect fibers,

### \* How the optical bus is connected:

Connect the Fibers to VMMR module. Make a power cycle to let all optical transceivers get active. At the other end of the fiber pairs you can now see light at one fiber.

Open the locker at MMR transceiver

MMR modulee with opened and closed locker

The fiber with red light has to be at the marked input (input arrow).

Insert the fiber pair into the transceiver (23 mm!!) until it hast contact to the internal optical units. Some times with new cables it clamps somewhere inside with its jacket. So check carefully if it can be inserted 23mm.

Close the locker to fix the fiber.

When the link is established, the red LED on the VMMR-bus should go off.

cutting, polishing of fibers

## Handling of thresholds,

### \* Why there are two thresholds?

If any channel of one MMR gets an amplitude above the **trigger threshold**, all channels are converted. Then the **data threshold** can be used to cut off noise (zeros) to reduce the amount of transmitted data.

### \* How to adjust the thresholds.

Usually adjust the threshold up until there are very few triggers.

\* The triggers can be seen at the green LEDs of the VMMR buses.

If the trigger rate has to be higher than can be checked by LED:

- \* set the trigger output to one bus and check with oscilloscope

- \* or check the rate of buses in the data acquisition.

For applications which require lowest threshold, some kHz of rate could be acceptable when a coincidence with the window of interest, triggered by an external low rate detector, can be established, or a very fast data acquisition allows readout of the large amount of data.

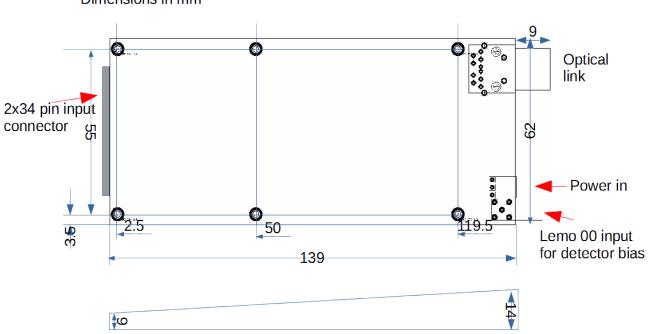

## **Power Supply**

MMR works from a single power supply of 6V to 8V ( + supply voltage at middle pin of the connector. The two other pins are ground)

MMR-64 typically 400 to 500mA, MMR-128 typically 900mA.

The crimp contacts are TE 927995-1 the crimp tool TE 726824-1 The connector shell: TE 928205-3

## **Dimensions, MMR-64**

## **Jumper setting from MMR SIP-Revision 1.7 (September 2021)**

The new revision provides more flexibility by choosing polarity and biasing mode for each group of 32 channels.

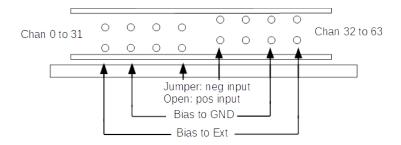

## **Jumper settings for MMR-64**

Bias to gnd means the preamp input is biased with ground level = 0V Jumper neg input: when the jumper is set the corresponding channels accept negative input charge. When open positive charge.

Bias to ext means: when jumper set the biasing network is connected to the bias Lemo input on the motherboard. Both neighbouring jumpers should not be jumpered. The unassigned position per 32 channel group should be left open.

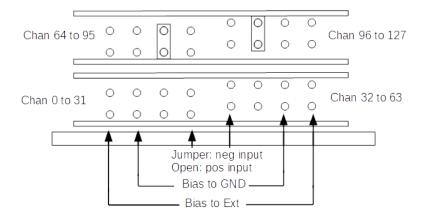

## **Jumper Settings for MMR-128**

All the same as MMR-64. The upper 64 channels are coded as high bank with two jumpers.