VMMR-8 / 16 (Data sheet V00.10)

## Hardware features:

## VMMR, the VME-receiver module

The VME receiver Module VMMR-8 / 16 has 8 or 16 optical buses. With 16 buses, 8 of them are back on the motherboard.

The module synchronises the front end clocks, receives triggers on the buses and accepts external gates. In specified coincidence cases the events are requested from the buses processed to a common event and store in a large memory. There it is available for VME readout. The event format is very similar to other mesytec modules like MDPP-16. Only the address space for more channels is larger.

The 16 bus module can receive up to 2048 channels. The number of VMMR VME modules in a setup is unlimited.

## **Optical Bus**

POF twin fiber to transmit up to 200 Mbit/s of data. Diameter of light guide = 1 mm, jacket diameter 2.2 mm. LED transmitter/receiver: 650 nm (red).

- Live insertion (can be inserted in a running crate)

- Power consumption: 6.5 W,

+5 V, 1.2 A

-12 V, 50 mA

# ATTENTION !!

## General for VME64X modules:

The locker screws of of the modules must be fixed for operation.

# **Control input / output**

- Differential control inputs:

- interface any differential signals: ECL, LVDS or LVPECL. They can be individually

- terminated (110  $\Omega$ ) via register settings

- NIM inputs:

- standard NIM, 50  $\Omega$

- NIM output:

- -0.7 V when terminated with 50  $\Omega$

- mesytec control bus output, shares connector with busy output. +0.7 V terminated

Minimum trigger width for individual inputs is = 10 ns Maximum external reference synchronization clock frequency (sync input): 75 MHz

# VMMR-16 register set, Data FIFO, read data at address 0x0000

## (access R/W D32, 64)

only even numbers of 32 bit-words will be transmitted. In case of odd number of data words, the last word will be a fill word (= 0).

FIFO size: 64k - 4k words with 32 bit length

## Header (4 byte)

|   | 2                   | 2         | 4         | 8         | 4   | 12                                               |

|---|---------------------|-----------|-----------|-----------|-----|--------------------------------------------------|

|   | header<br>signature | subheader |           | module id |     | number of following data words,<br>including EOE |

| Į | b01                 | b00       | b000,trig | module id | 0x0 | number of 32 bit data words                      |

## Data (4 byte) DATA event

| 2<br>data-sig | 2  | 4          | 8    | 16                                           |

|---------------|----|------------|------|----------------------------------------------|

| b00           | 10 | Bus Number | 0x00 | Time difference<br>Gate start to bus trigger |

#### Data (4 byte) DATA event

| 2        | 2  | 4          | 12                   | 12        |

|----------|----|------------|----------------------|-----------|

| data-sig |    |            |                      |           |

| b00      | 01 | Bus Number | Front end subaddress | ADC value |

#### Data (4 byte) Extended time stamp

| 2        | 2  | 12             | 16                         |

|----------|----|----------------|----------------------------|

| data-sig |    |                |                            |

| b00      | 10 | XXXX 1XXX XXXX | 16 high bits of time stamp |

## Data (4 byte), fill dummy (to fill MBLT64 word at odd data number)

| 2        | 30 |

|----------|----|

| data-sig |    |

| b00      | 0  |

#### End of Event marker (4 byte)

| 2   | 30                         |

|-----|----------------------------|

| b11 | event counter / time stamp |

# Registers, Starting at address x6000 (access D16)

| Address | Name              | Bits | dir | default | Comment                                         |

|---------|-------------------|------|-----|---------|-------------------------------------------------|

|         | Address registers |      |     |         |                                                 |

| 0x6000  | address_source    | 1    | RW  | 0       | 0 = from board coder, 1 from address_reg        |

| 0x6002  | address_reg       | 16   | RW  | 0       | address to override decoder on board            |

| 0x6004  | module_id         | 8    | RW  | 0xFF    | is part of data header                          |

|         |                   |      |     |         | If value = FF, the 8 high bits of base address  |

|         |                   |      |     |         | are used (always board coder).                  |

| 0x6006  | Fast MBLT         | 1    | W   | 1       | 0 = reduce MBLT cycle time to 100ns             |

| 0x6008  | soft_reset        | 1    | RW  |         | breaks all activities, sets critical parameters |

|         |                   |      |     |         | to default. Wait 200 ms after writing           |

|         |                   |      |     |         | this register.                                  |

|         |                   |      |     |         | read: Hardware index: 0x5006                    |

| 0x600E  | firmware_revision | 16   | R   |         | Example: rev $1.4 = 0x0104$                     |

|        | IRQ (ROACK)         |    |    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------------------|----|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6010 | irq_level           | 3  | RW | 0 | IRQ priority $17$ , $0 = IRQ$ off                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0x6012 | irq_vector          | 8  | RW | 0 | IRQ return value                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x6014 | irq_test            | 0  | W  |   | initiates an IRQ (for test)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x6016 | irq_reset           | 0  | W  |   | resets IRQ (for test)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0x6018 | irq_data_threshold  | 15 | RW | 1 | Every time the number of 32 bit words in the<br>FIFO exceeds this threshold, an IRQ is<br>emitted. Maximum allowed threshold is<br>"FIFO size".                                                                                                                                                                                                                                                                                                                                    |

| 0x601A | Max_transfer_data   | 15 | RW | 1 | <ol> <li>Specifies the amount of <b>data</b> read from<br/>FIFO before Berr is emitted. Only active for<br/>multi <b>event mode 3</b>.<br/>Transfer is stopped only after full events.<br/>Example: At Max_transfer_data = 1, 1 event<br/>per transfer is emitted.</li> <li>Specifies the number of <b>events</b> read<br/>from FIFO before Berr is emitted.<br/>Active for multi <b>event mode 0xb.</b></li> <li>Setting the value to 0 allows unlimited<br/>transfer.</li> </ol> |

| 0x601C | IRQ_source          | 1  | RW | 1 | IRQ source:<br>0 = <b>event</b> threshold exceeded<br>1 = <b>data</b> threshold exceeded                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x601E | irq_event_threshold | 15 | RW | 1 | Every time the number of events in the FIFO exceeds this threshold, an IRQ is emitted.                                                                                                                                                                                                                                                                                                                                                                                             |

For multi event mode 2 and 3 the IRQ is:

- set when the FIFO fill level gets more than the threshold and is

- withdrawn when IRQ is acknowledged or when the fill level goes below the threshold

<u>Amesytec</u>

# VMMR-8 / 16

|        | MCST CBLT         |   |    |      |                      |

|--------|-------------------|---|----|------|----------------------|

| 0x6020 | cblt_mcst_control | 8 | RW | 0    | see table            |

| 0x6022 | cblt_address      | 8 | RW | 0xAA | A31A25 CBLT- address |

| 0x6024 | mcst_address      | 8 | R  | 0xBB | A31A25 MCST- address |

| Bit | Name     | Write                                                    | Read                                                                                       |

|-----|----------|----------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 7   | MCSTENB  | Enable MCST     No effect                                | 0                                                                                          |

| 6   | MCSTDIS  | 1 Disable MCST     0 No effect                           | <ol> <li>MCST enabled</li> <li>MCST disabled</li> </ol>                                    |

| 5   | FIRSTENB | 1 Enable first module<br>in a CBLT chain<br>0 No effect  | 0                                                                                          |

| 4   | FIRSTDIS | 1 Disable first module<br>in a CBLT chain<br>0 No effect | <ol> <li>First module in a CBLT chain</li> <li>Not first module in a CBLT chain</li> </ol> |

| 3   | LASTENB  | 1 Enable last module<br>in an CBLT chain<br>0 No effect  | 0                                                                                          |

| 2   | LASTDIS  | 1 Disable last module<br>in an CBLT chain<br>0 No effect | <ol> <li>Last module in a CBLT chain</li> <li>Not last module in a CBLT chain</li> </ol>   |

| 1   | CBLTENB  | 1 Enable CBLT<br>0 No effect                             | 0                                                                                          |

| 0   | CBLTDIS  | 1 Disable CBLT<br>0 No effect                            | 1CBLT enabled0CBLT disabled                                                                |

#### **CBLT Address Field**

| A31A24    | A23A00                                                     |

|-----------|------------------------------------------------------------|

| CBLT ADRS | 8 high bits, not significant + 16 bit module address space |

## **MCST Address Field**

| A31A24    | A23A00                                                     |

|-----------|------------------------------------------------------------|

| MCST ADRS | 8 high bits, not significant + 16 bit module address space |

## At BLT32

When an empty module is accessed at address 0, BERR is emitted.

## At CBLT

When no module contains data, no data are transmitted. The last module emits BERR.

|        | FIFO handling      |    |    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                           |                                                                                                                                               |

|--------|--------------------|----|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6030 | buffer_data_length | 16 | R  |   | amount of data in FIFC<br>(only fully converted e<br>Units → data_len_form<br>Can be used for single                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vents).<br>iat.<br>- and multi ev                                                                                                                                         |                                                                                                                                               |

| 0x6032 | data_len_format    | 2  | RW | 2 | 0 = 8 bit, 1 = 16 bit, 2<br>4 = show number of e<br>The number of 32 bit v<br>If necessary the fill wo<br>For len 0 and 1 the may<br>when number exceeds<br>The FIFO is not affected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | vents in FIFO.<br>words is alway<br>ord "0" is adde<br>ax value 0xFFF<br>the 16 bit for                                                                                   | rs even.<br>d.<br>F is shown                                                                                                                  |

| 0x6034 | readout_reset      |    | W  |   | At single event mode (<br>trigger, allow IRQ<br>At multi event = <b>1</b> : ch<br>when enough data. All<br>buffer fill level does no<br>threshold at readout.<br>At multievent = <b>3</b> : clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | multi event =<br>ecks threshold<br>ows safe oper<br>t go below the                                                                                                        | l, sets IRQ<br>ation when<br>e data                                                                                                           |

| 0x6036 | multi event        | 4  | RW | 0 | Bit [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit [2]                                                                                                                                                                   | Bit [1:0]                                                                                                                                     |

|        |                    |    |    |   | count events<br>not words<br>(reg. 0x601A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | skip berr,<br>send EOB                                                                                                                                                    | mode [1:0]                                                                                                                                    |

|        |                    |    |    |   | Allow multi event buffer<br><b>mode = 0</b> $\rightarrow$ <b>no</b> (0x6<br>conversion)<br><b>mode = 1</b> $\rightarrow$ <b>yes</b> , unlereset required (0x6034<br>readout). Don't use for<br><b>mode = 3</b> $\rightarrow$ <b>yes</b> but<br>amount of data. With the<br>data words can be specified at the set of the set | 034 clears even<br>imited transfe<br>can be writted<br>or CBLT<br>VMMR transfe<br>reg 0x601A th<br>ccified. After w<br>of event mark<br>err. So 0x601A<br>r (Berr after e | ent, allows new<br>r, no readout<br>en after block<br>ers limited<br>e number of<br>ord limits is<br>a terminates<br>= 1 means<br>ach event). |

|        |                    |    |    |   | <b>Berr handling:</b> when<br>Send EOB = bit [31:30<br>Bit [3]: Compare numb<br>(not words!) with max<br>for Berr condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ] = bx10 inste<br>per of transmit                                                                                                                                         | ted events                                                                                                                                    |

| 0x6038 | marking_type       | 2  | RW | 0 | $\begin{array}{l} 00 \rightarrow \text{event counter} \\ 01 \rightarrow \text{time stamp} \\ 11 \rightarrow \text{extended time st} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | amp                                                                                                                                                                       |                                                                                                                                               |

|        |                    |    |    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                           | → next page                                                                                                                                   |

| 0x603A | start_acq  | 1 | RW | 1 | $1 \rightarrow$ start accepting triggers<br>If no external trigger logic, which stops the gates<br>when daq is not running, is implemented, this<br>register should be set to 0 before applying the<br>FIFO_reset to get a well defined status.<br>When setting it to 1 again for data acquisition<br>start, the module is in a well defined status. |

|--------|------------|---|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x603C | FIFO_reset |   | W  |   | Initialize FIFO                                                                                                                                                                                                                                                                                                                                      |

| 0x603E | data_ready | 1 | R  |   | $1 \rightarrow$ data available                                                                                                                                                                                                                                                                                                                       |

|        | operation mode                                  |    |    |        |                                                                                                                                                                    |

|--------|-------------------------------------------------|----|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6040 | bus_ok                                          | 16 | R  |        | At acquisition start, VMMR evaluates buses if<br>they are connected. Result in binary representa-<br>tion: For example 0b000000000000011, bus0,1<br>are connected. |

| 0x6042 | active_buses                                    | 16 | RW | 0xFFFF | a 1 means bus active, read: activated buses at start_daq                                                                                                           |

| 0x6046 | Timing resolution<br>(SW-RevX110 and<br>higher) | 1  | RW | 0      | Set timing resolution $5ns = 0$ ; $1ns = 1$ .<br>1ns setting requires MMR mudules with 1ns reso-<br>lution. Trigger input with 1ns res., trigger out 5ns<br>res.   |

| 0x604C | Gate_blocking_time                              | 11 | RW | 0      | multiples of 10ns; Gate can be blocked for this time.                                                                                                              |

|        | Trigger            |    |    |               |                                                                                                                                                                                                                           |

|--------|--------------------|----|----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6050 | win_start          | 13 | RW | 0x1000<br>-32 | Unit: 5 ns<br>Start window of interest:<br>0x0000 start at -20.48 us<br>0x1FFF start at +20.48 us<br>0x1000 = 4k, no delay<br>< 4k, window starts before Trigger<br>> 4k, window is delayed                               |

| 0x6054 | win_width          | 12 | RW | 64            | Unit: 5 ns, max $4k = 20.48$ us                                                                                                                                                                                           |

| 0x6058 | ext_trig_source    | 2  | RW | 3             | trig1 / trig0 to trigger gate                                                                                                                                                                                             |

| 0x605A | trig_source        | 16 | RW | 0             | this register allows to set any number of<br>individual MMR-Frontends (buses) creating the<br>trigger.<br>Bit 0 corresponds to bus 0, bit 15 to bus 15. A<br>"1" marks the buses as trigger source.                       |

| 0x605C | out_trigger_source | 1  | RW | 0             | <ul> <li>0 = free trigger to trigger output (standard operation)</li> <li>1 = output triggers which are accepted by window of interest (can be useful when self triggered and MVLC is the only trigger source)</li> </ul> |

| 0x605E | trigger_output     | 8  | RW | 0x00          | If 0x605C = 0 (selects free trigger):<br>Bit 0 corresponds to bus 0, bit 15 to bus 15. A<br>"1" marks the bus as trigger source.                                                                                          |

| IO<br>0x6060 | Inputs, outputs |   |    |      |                                                         |

|--------------|-----------------|---|----|------|---------------------------------------------------------|

| 0x6060       | ECL3            | 8 | RW | 0x00 | INPUT                                                   |

|              |                 |   |    |      | lower 4 bit: $0 = Off$ , $1 = Trig0$ in                 |

|              |                 |   |    |      | higher 4 bit: 0 = terminated, 1 = unterminated          |

| 0x6062       | ECL2            | 8 | RW | 0x00 | INPUT                                                   |

|              |                 |   |    |      | lower 4 bit: $0 = Off$ , $1 = Sync_in$ , $2 = Trig1$ in |

|              |                 |   |    |      | higher 4 bit: 0 = terminated, 1 = unterminated          |

|              |                 |   |    |      | when sync is selected also set reg 0x6096 !!            |

| 0x6064       | ECL1            | 8 | RW | 0x00 | INPUT                                                   |

|              |                 |   |    |      | lower 4 bit: $0 = Off$ , $1 = Reset_in$                 |

|              |                 |   |    |      | higher 4 bit: 0 = terminated, 1 = unterminated          |

| 0x6066       | ECL0            | 4 | RW | 0    | OUTPUT                                                  |

|              |                 |   |    |      | 0 = Off, 4 = Busy,                                      |

|              |                 |   |    |      | 8 = data in buffer above threshold 0x6018               |

|              |                 |   |    |      | (= Data ready)                                          |

|              |                 |   |    |      | 9 = events in buffer above threshold 0x601E             |

| 0x6068       | NIM3            | 2 | RW | 1    | INPUT                                                   |

|              |                 |   |    |      | $0 = Off, 1 = Trig0_in, 2 = sync_in$                    |

|              |                 |   |    |      | when sync is selected also set reg 0x6096 !!            |

| 0x606A       | NIM2            | 2 | RW | 1    | 0 = off, 1 = Trig1_in, 2 = timestamp_reset              |

| 0x606C       | NIM1            | 4 | XX | X    | 1 = trig_out, 5= NIM Trigger group 1 out                |

| 0x606E       | NIM0            |   |    |      | 0 = Off, 1 = Cbus,                                      |

|              |                 |   |    |      | 4 = Busy_out (= FIFO full or ACQ stopped)               |

|              |                 |   |    |      | 5= NIM Trigger group 0 out                              |

|              |                 |   |    |      | 8 = data in buffer above threshold 0x6018               |

|              |                 |   |    |      | 9 = events in buffer above threshold 0x601E             |

The test pulses are generated in MMR frontends and are injected at the inputs of the preamps. They are initiated by a ping signal on the buses which is centrally created by the VMMR with a frequency of 6kHz. So pulses are created absolutely synchronous in all connected MMRs.

When "only triggers" is set, the MMRs start conversion without injecting a pulser signal. So only noise is converted.

| 0x6070 | Test pulser      |   |    |     |                                                                     |

|--------|------------------|---|----|-----|---------------------------------------------------------------------|

| 0x6070 | pulser_status;   | 1 | RW | 0   | 0 = Off, 1 = Pulser on (6kHz),                                      |

|        |                  |   |    |     | $(3 = \text{send triggers only} \rightarrow \text{read pedestals})$ |

| 0x6072 | pulser_amplitude | 8 | RW | 100 | maximum amplitude: 0xFF = 255                                       |

|        |                  |   |    |     |                                                                     |

# **IO selection Overview**

The numbers in the table can be written to the corresponding register. For example: ECL2 should input the trigger 1: write 2 to 0x6062.

| ю    | default | TR0 | TR1 | SYN | RES | TRout | Busy | T1_out<br>T0_out | Rdy<br>data | Rdy<br>event | Cbus |

|------|---------|-----|-----|-----|-----|-------|------|------------------|-------------|--------------|------|

| ECL3 | 0       | 1   |     |     |     |       |      |                  |             |              |      |

| ECL2 | 0       |     | 2   | 1   |     |       |      |                  |             |              |      |

| ECL1 | 0       |     |     |     | 1   |       |      |                  |             |              |      |

| ECL0 | 0       |     |     |     |     |       | 4    |                  | 8           | 9            |      |

| NIM3 | 1       | 1   |     | 2   |     |       |      |                  |             |              |      |

| NIM2 | 1       |     | 1   |     | 2   |       |      |                  |             |              |      |

| NIM1 | 1       |     |     |     |     | 1     |      | 5                |             |              |      |

| NIM0 | 1       |     |     |     |     |       | 4    | 5                | 8           | 9            | 1    |

Selection of 0 always means it is unused or "Off"

## Description

T1\_out/T0\_out: trigger from group selected by reg 631A for NIM0, by reg 631C for NIM1

- TR0 = Trigger 0 input

- TR1 = Trigger 1 input

- SYN = external Frequency to synchronize event time stamp

- RES = reset for event time stamp

- TRout = trigger output

- Busy = module not ready to take more triggers

- Rdy dat = data in buffer above threshold register "0x6018"

- Rdy eve = events in buffer above threshold register "0x601E"

- Cbus = control bus to control external mesytec modules (MHV-4, MPRB-32...)

# Mesytec control bus:

| MRC<br>0x6080 | Module RC          |    |    |   |                                                                                             |

|---------------|--------------------|----|----|---|---------------------------------------------------------------------------------------------|

| 0x6080        | rc_busno           | 2  | RW | 0 | 0 is external bus, comes out at busy output                                                 |

| 0x6082        | rc_modnum          | 4  | RW | 0 | 015<br>(module ID set with hex coder at external module)                                    |

| 0x6084        | rc_opcode          | 7  | RW |   | $3 = RC_on, 4 = RC_off, 6 = read_id,$<br>16 = write_data, 18 = read_data                    |

| 0x6086        | rc_adr             | 8  | RW |   | module internal address, see box below                                                      |

| 0x6088        | rc_dat             | 16 | RW |   | data (send or receive), write starts sending                                                |

| 0x608A        | send return status | 4  | R  |   | bit0 = active<br>bit1 = address collision<br>bit2 = no response from bus (no valid address) |

Send time is 400 us. Wait that fixed time before reading response or sending new data. Also polling at 0x608A for bit0 = 0 is possible

The Trigger0-LED shows data traffic on the bus, the Trigger1-LED shows bus errors (i.e. non terminated lines)

## Example for controlling external modules with mesytec RC-bus

Initialize and read out a MCFD-16 CFD- module. MCFD-16 ID-coder set to 7 Bus line must be terminated at the far end.

## Activate VMMR control bus at busy line

Write(16) addr 0x6074 data 1

## Get Module ID-Code (= Type of module = 26 for MCFD-16)

| Write(16) | addr 0x6082 data 7 | // address module 7                            |

|-----------|--------------------|------------------------------------------------|

| Write(16) | addr 0x6084 data 6 | // send code "read IDC"                        |

| Write(16) | addr 0x6088 data 0 | // initialize send request. Data has no effect |

Wait loop: Read(16) 0x608A and compare bit0 to get 0. Then evaluate other bits for error status

| Read(16) | addr 0x6088 data 40 | // at ID readout the bit 0 shows the module RC status |

|----------|---------------------|-------------------------------------------------------|

|          |                     | // (1 is on). Bit 17 show the IDC                     |

|          |                     | $// \rightarrow$ interpretation: Module off, IDC = 20 |

#### Set threshold for channel 0 to 10

| Write(16) | addr 0x6082 data 7  | // address module 7                 |

|-----------|---------------------|-------------------------------------|

| Write(16) | addr 0x6084 data 16 | // code "write_data"                |

| Write(16) | addr 0x6086 data 0  | // address module memory location 1 |

| Write(16) | addr 0x6088 data 10 | // start send. Data to send         |

Wait loop: Read(16) 0x608A and compare bit0 to get 0. Then evaluate other bits for error status.

Optional the read back data is available Read(16) addr 0x6088 data 10 // read back written data for control

## Read threshold of channel 0

| Write(16) | addr 0x6082 data 7  | // address module 7                      |

|-----------|---------------------|------------------------------------------|

| Write(16) | addr 0x6084 data 18 | // code "read_data"                      |

| Write(16) | addr 0x6086 data 0  | // address module memory location 1      |

| Write(16) | addr 0x6088 data 0  | // send read request. Data has no effect |

Wait loop: Read(16) 0x608A and compare bit0 to get 0. Then evaluate other bits for error status

Read(16) addr 0x6088 data 10 // read out data, "10" returned

## Activate RC in module

All set data will get active. This can also be done before setting the values.

| Write(16) | addr 0x6082 data 7 | // address module 7                            |

|-----------|--------------------|------------------------------------------------|

| Write(16) | addr 0x6084 data 3 | // send code "RC_on"                           |

| Write(16) | addr 0x6088 data 0 | // initialize send request. Data has no effect |

#### Deactivate VMMR-16 control bus at busy line

Write(16) addr 0x606E data 0 // busy output used as busy

# CTRA

Time stamp counters, event counters

All counters have to be read in the order: low word then high word !!!

They are latched at low word read. The event counter counts events which are written to the buffer.

| CTRA<br>0x6090 | counters A    |    |    |     |                                                                                                                                                                                                                                                                                              |

|----------------|---------------|----|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6090         | Reset_ctr_ab  | 2  | RW |     | b0001 resets all counters in CTRA,<br>b0010 resets all counters in CTRB,<br>b1100 allows single shot reset for CTRA<br>with first edge of external reset signal.<br>the bit bx1xx is reset with this first edge<br>Reset of "counters A" will also reset the global<br>46 bit TDC time stamp |

| 0x6092         | evctr_lo      | 16 | R  | 0   | event counter low value                                                                                                                                                                                                                                                                      |

| 0x6094         | evctr_hi      | 16 | R  | 0   | event counter high value                                                                                                                                                                                                                                                                     |

| 0x6096         | ts_sources    | 5  | RW | b00 | bit0: frequency source (VME = 0, external = 1)<br>bit1: external reset enable = 1<br>bit4: CTRB "time" counts trigger outputs<br>(= free triggers, selected by 0x605E)                                                                                                                       |

| 0x6098         | ts_divisor    | 16 | RW | 1   | time stamp = time / (ts_divisor)<br>0 means division by 65536                                                                                                                                                                                                                                |

| 0x609C         | ts_counter_lo | 16 | R  |     | Time low value                                                                                                                                                                                                                                                                               |

| 0x609E         | ts_counter_hi | 16 | R  |     | Time high value                                                                                                                                                                                                                                                                              |

## CTRB

Counters are latched when VME is reading the low word Output value is divided by 40 to give a 1 us time basis

| CTRB<br>0x60A0 | counters B |    |    |   |                                                                                                 |

|----------------|------------|----|----|---|-------------------------------------------------------------------------------------------------|

| 0x60A8         | time_0     | 16 | R  |   | Time [1 us] (48 bit)<br>RCP: alternately: free triggers, selected by 0x6096<br>bit4, and 0x605E |

| 0x60AA         | time_1     | 16 | R  |   |                                                                                                 |

| 0x60AC         | time_2     | 16 | R  |   |                                                                                                 |

| 0x60AE         | stop_ctr   | 2  | RW | 0 | 0 = run, 1 = stop counter<br>bit 0 all counter B<br>bit 1 time stamp counter (A)                |

## **Bus addressing**

| 0x6100 | select_Bus | 4 | RW | 0 | 015 selects individual buses,                  |

|--------|------------|---|----|---|------------------------------------------------|

|        |            |   |    |   | 16 selects all (only write to bus is possible) |

| Address<br>0x6110 | Parameter    |    |    | default |                                                                                                                                     |

|-------------------|--------------|----|----|---------|-------------------------------------------------------------------------------------------------------------------------------------|

| 6110              | fe_addr_wr   | 8  | RW | 0       | Set Write subaddress in Frontend                                                                                                    |

| 6112              | fe_data_wr   | 16 | W  |         | Data write register, <b>starts write</b> .<br>Write needs up to 650ns, independent of 1 or all buses<br>write. buffer FIFO 32 Words |

| 6114              | fe_addr_rd   | 8  | W  |         | Read subadress data in Frontend, <b>starts read</b> .<br>Result is written into an output FIFO (delay 2 us);<br>Fifo depth 32 words |

| 6116              | Read_Address | 8  | R  |         | read FIFO: Frontend: {4'h0,bus[3:0],Address [7:0]}<br>Empty FIFO returns 0xFFFF                                                     |

| 6118              | Read_Data    | 16 | R  |         | read FIFO Frontend Data [15:0], and release next data.<br>Empty FIFO returns 0xFFFF                                                 |

| 611A              | bus_delay    | 9  | R  | 50      | longest bus in [m], 050 allowed.<br>50m always works.                                                                               |

# Frontend module registers

| 0x01 | reset          | 0  | W  | resets front end data                                                                                                                                                                                                                                                              |

|------|----------------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x03 | LEDs_on        | 1  | W  | onboard LEDs activated (switch off for light sensitive de-<br>tectors)                                                                                                                                                                                                             |

| 0x04 | start          | 1  | W  | accept trigger, stop also clears buffers                                                                                                                                                                                                                                           |

| 0x05 | temp           | 12 |    | multiples of 0.1 °C                                                                                                                                                                                                                                                                |

| 0x06 | voltage        | 12 |    | primary voltage, multiples of 100 mV                                                                                                                                                                                                                                               |

| 0x07 | receive_power  | 12 |    | Amount of received light on optical bus (arbitrary units)                                                                                                                                                                                                                          |

| 0x08 | Pulser_Ampl    | 8  |    | DACA: pulser amplitude                                                                                                                                                                                                                                                             |

| 0x09 | com_thr0       | 8  |    | DACB, trigger threshold, usually lower 32 channels, assigned application specific.                                                                                                                                                                                                 |

| 0x0A | com_thr1       | 8  |    | DACC, trigger threshold, usually higher 32 channels, assigned application specific.                                                                                                                                                                                                |

| 0x0B | aux_thr1       | 8  |    | DACD, trigger threshold, usually 64 high channels for MMR128, assigned application specific.                                                                                                                                                                                       |

| 0x0C | Pulser_ping    | 2  | 00 | Usually use central pulser (reg 0x6070), leave this<br>register at default!; default setting b00 = off<br>b00 $\rightarrow$ one pulser ping; b01 $\rightarrow$ one trigger ping;<br>b10 $\rightarrow$ periodic pulser; b11 $\rightarrow$ periodic trigger;<br>Local pulser 1.2kHz; |

| 0x10 | data_threshold | 12 |    | For all MMR-channels, data below are suppressed                                                                                                                                                                                                                                    |

| 0x21 | peak_delay     | 8  |    | maximum possible delay between trigger and shaper peak<br>Multiples of 10ns                                                                                                                                                                                                        |

| 0x22 | active_bank    | 16 |    | Factory setting, do not write.<br>{tp3[3:0],tp2[3:0],tp1[3:0],tp0[3:0]} def: 0x0021 -> lower two banks; 0x8421 $\rightarrow$ all 4 banks                                                                                                                                           |

| 0x23 | bus_error      | 16 |    | bit errors occured on optical bus. Write: reset 0x23, 0x24                                                                                                                                                                                                                         |

| 0x24 | PLL Error         | 16 | Desynchronisation count of PLL; |

|------|-------------------|----|---------------------------------|

| 0x30 | Firmware_revision | 16 | 0x0006, 0x0007 Hex notation!    |

| 0x31 | Hardware Revision | 16 | 0x0014, 0x0015 Hex notation!    |

## Read a register value from MMR connected to optical bus: Request data

0x6100 Bus\_Number 0x6114 Register\_address 0x6114 Register\_address // select the bus number to request data

// select the register number in MMR module

Repeat Register request maximum 25 times, also different buses are possible the request can also be sent to all buses by selecting bus number = 16. This initiates up to 16 registers to be read out. So for an VMMR-16 with all buses occupied it results in reading 16 registers.

Wait at least 1ms

#### Get data from FIFO (depth max 30 register contents). The requsted data are now in a FIFO:

0x6116 {bus\_number[3:0], reg\_Address[7:0]} 0x6118 Data[15:0] gets register content data from FIFO, requests next data from FIFO

#### Write a register value to MMR connected to optical bus:

16 cmds per bus, then wait some us. Bus address 16 "to all" cmds may be sent.

0x6100 Bus\_Number[3:0] // to bus 0..15 or to all = 16 0x6110 Register addressing[7:0] 0x6112 Data to write[15:0] and start send

# **Special Trigger outputs**

Starting with March 2021 a new feature is built into all firmware. The VME IRQ lines are mostly unused, but are very good high quality lines to the VME controller. A combination of input triggers can be sent to the 7 available IRQ lines, and can be processed in the Trigger IO of the MVLC controller. A collision of signals with other IRQ signaling of the module should be avoided. Several modules may control the same IRQ line, the outputs are then a wired OR of all participating modules. Pulse length is fixed 50ns.

| VME-<br>Addr | Name         | Width | Direc-<br>tion | Value  | Description                                                                                                                                            |

|--------------|--------------|-------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x6300       | Trig to IRQ1 | 16    | RW             | 0x0000 | Connect an OR of the selected bus triggers<br>(up to 16) to IRQ line 1. Example<br>0b00000000 10000001 means bus 0 and 7<br>are Ored and sent to IRQ 1 |

| 0x6304       | Trig to IRQ2 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x6308       | Trig to IRQ3 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x630C       | Trig to IRQ4 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x6310       | Trig to IRQ5 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x6314       | Trig to IRQ6 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x6318       | Trig to IRQ7 | 16    | RW             | 0x0000 |                                                                                                                                                        |

| 0x631C       | Trig_NIM0    | 16    | RW             | 0x0000 | NIM Trigger group 0                                                                                                                                    |

| 0x6320       | Trig_NIM1    | 16    | RW             | 0x0000 | NIM Trigger group 1                                                                                                                                    |

## FAQ:

#### \* Why there are two thresholds ?

If any channel of one MMR gets an amplitude above the **discriminator threshold**, all channels are converted. Then the **data threshold** can be used to cut off noise (zeros) to reduce the amount of transmitted data.

#### \* How to adjust the thresholds.

Usually adjust the threshold up until there are very few triggers per second. \* The triggers can be seen at the green LEDs of the VMMR buses.

If the trigger rate has to be higher than can be checked by LED:

\* set the trigger output to one bus and check with oscilloscope

\* or check the rate of buses in the data acquisition.

For applications which require lowest threshold, some kHz of rate could be acceptable when a coincidence with the window of interest, triggered by an external low rate detector, can be established, or a very fast data acquisition allows readout of the large amount of data.

#### \* How the optical bus is connected:

Connect the Fibers to VMMR module. Make a power cycle to let all optical transceivers get active. At the other end of the fiber pairs you can now see light at one fiber.

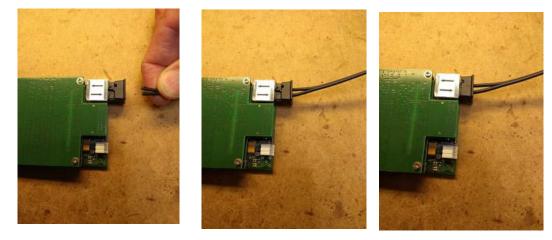

Open the locker at MMR transceiver

MMR modulee with opened and closed locker

The fiber with red light has to be at the marked input (input arrow). Insert the fiber pair into the transceiver (23 mm !!) until it hast contact to the internal optical units. Some times with new cables it clamps somewhere inside with its jacket. So check carefully if it can be inserted 23mm. Close the locker to fix the fiber. When the link is established, the red LED on the VMMR-bus should go off.